MOS 4027 – Ihr Kernstück für präzise digitale Logikschaltungen

Sie suchen nach einer zuverlässigen Lösung für die Realisierung von Zustandsänderungen und die Speicherung von Bits in digitalen Systemen? Der MOS 4027 – ein dualer JK-Flip-Flop – ist die essenzielle Komponente, die Entwickler von Mikrocontrollern, Lernprojekten und spezialisierten Elektronikanwendungen benötigen, um komplexe Logikfunktionen aufzubauen. Dieses IC bietet eine robuste und vielseitige Basis für die Synchronisation von Taktgebern, den Aufbau von Zählern oder die Implementierung von Speicherelementen.

Überlegene Leistung und Zuverlässigkeit des MOS 4027 JK-Flip-Flop

Im Vergleich zu einfacheren D-Flip-Flops oder weniger integrierten Lösungen bietet der MOS 4027 JK-Type entscheidende Vorteile. Seine Fähigkeit, sowohl auf steigende als auch auf fallende Taktflanken zu reagieren, kombiniert mit den steuerbaren Set- und Reset-Eingängen, ermöglicht eine wesentlich flexiblere und präzisere Steuerung des Schaltzustands. Dies minimiert das Risiko von Race Conditions und unerwarteten Zustandsänderungen, was ihn zur überlegenen Wahl für anspruchsvolle Schaltungsdesigns macht.

Fundamentale Funktionsweise und Anwendungsszenarien

Der MOS 4027 ist ein integrierter Schaltkreis, der zwei unabhängige JK-Flip-Flops in einem einzigen Gehäuse vereint. Jeder JK-Flip-Flop verfügt über Eingänge für Clock (Takt), Set (S), Reset (R), J und K. Das Verhalten des Flip-Flops wird durch die Kombination der J- und K-Eingänge bestimmt, während der Takt die Zustandsänderung auslöst. Die Set- und Reset-Eingänge ermöglichen eine direkte Manipulation des Zustands, unabhängig vom Takt, was für die Initialisierung oder Fehlerkorrektur unerlässlich ist. Dieser duale Aufbau ermöglicht den gleichzeitigen Betrieb zweier unabhängiger Speicherelemente, was die Effizienz in der Schaltungsentwicklung steigert.

Die Kernvorteile des MOS 4027 im Überblick:

- Vielseitige Logikfunktionen: Implementieren Sie komplexe Schaltungen wie Taktgeber-Teiler, Schieberegister, Zähler und Zustandsautomaten.

- Hohe Störfestigkeit: Die CMOS-Technologie gewährleistet eine gute Immunität gegenüber externen Störsignalen, was zu stabilen Schaltungsergebnissen führt.

- Breiter Betriebsspannungsbereich: Mit 3 V bis 15 V passt sich der MOS 4027 flexibel an verschiedene Stromversorgungen an, von batteriebetriebenen Geräten bis hin zu anspruchsvolleren Systemen.

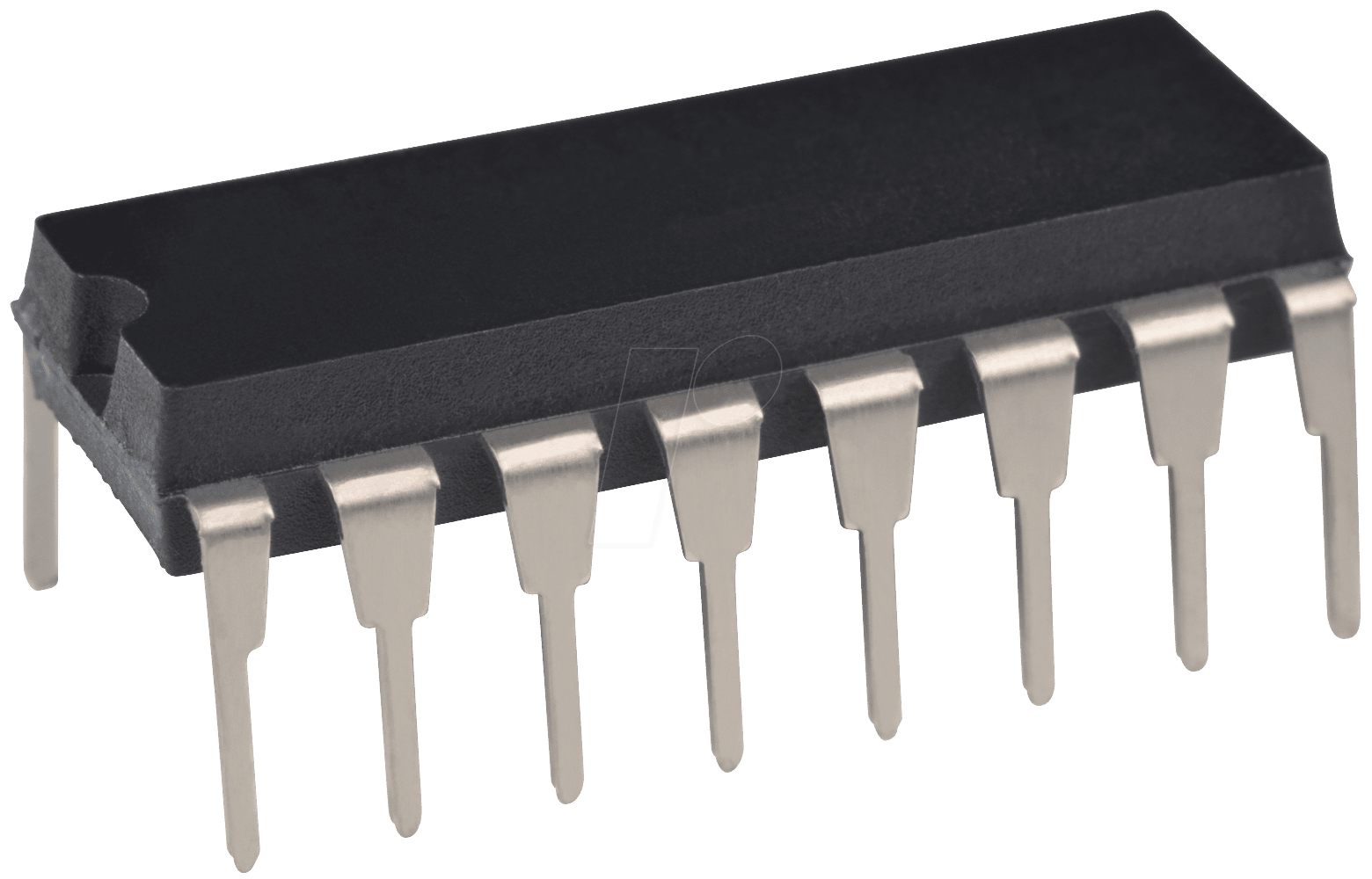

- Einfache Integration: Das bewährte DIP-16 Gehäuse ermöglicht eine einfache Bestückung auf Lochrasterplatinen und in gängigen Stecksystemen.

- Zwei unabhängige Flip-Flops: Maximale Effizienz durch die Integration zweier funktionaler Einheiten pro IC.

- Asynchrone Set- und Reset-Funktionen: Direkte Zustandsmanipulation zur einfachen Initialisierung und Fehlerbehandlung.

- Synchroner Betrieb: Präzise und vorhersagbare Zustandsänderungen, synchronisiert mit der Taktflanke.

Detaillierte technische Spezifikationen

| Merkmal | Beschreibung |

|---|---|

| IC-Typ | Dual JK-Flip-Flop |

| Modellnummer | MOS 4027 (entspricht CD4027B) |

| Logikfamilie | CMOS |

| Betriebsspannung | 3 V bis 15 V DC |

| Anzahl der Flip-Flops | 2 |

| Taktung | Steigende und fallende Taktflanken-gesteuert |

| Steuereingänge pro Flip-Flop | J, K, Clock, Set (S), Reset (R) |

| Ausgänge pro Flip-Flop | Q und Q-nicht (komplementär) |

| Gehäuse | DIP-16 (Dual In-line Package, 16 Pins) |

| Stromaufnahme (typisch) | Sehr gering im statischen Betrieb (typisch einige nA bis wenige µA bei 5V, abhängig von der genauen Variante und Hersteller). Strom steigt mit der Taktfrequenz und Betriebsspannung. |

| Betriebstemperaturbereich | Variiert je nach Hersteller, typischerweise -55°C bis +125°C für industrielle Varianten. Gängige kommerzielle Varianten liegen oft bei -40°C bis +85°C. |

| Anschluss-Layout | Standardbelegung für 16-polige DIP-ICs, leicht auf Steckplatinen (Breadboards) zu verwenden. |

Technische Tiefe und Konstruktionsprinzipien

Der MOS 4027 basiert auf der Complementary Metal-Oxide-Semiconductor (CMOS)-Technologie, die ihm eine exzellente Energieeffizienz und eine hohe Rauschunterdrückung verleiht. Die interne Struktur jedes JK-Flip-Flops nutzt Transistoren, um zwei stabile Zustände (0 oder 1) zu speichern. Die J- und K-Eingänge sind so konfiguriert, dass sie jede mögliche Kombination von Eingangslogik verarbeiten und den Ausgang entsprechend der Taktflanke aktualisieren. Insbesondere die JK-Funktionalität, bei der J=1 und K=1 zu einem „Toggle“-Zustand führt (Umschalten des Ausgangs), ist für den Aufbau von Zählern unerlässlich. Die asynchronen Set- und Reset-Eingänge (S und R) umgehen den synchronen Taktmechanismus und ermöglichen eine sofortige Einstellung des Zustands, was für das Zurücksetzen von Registern oder die Synchronisation von Systemen nach einem Neustart von entscheidender Bedeutung ist. Die komplementären Ausgänge (Q und Q-nicht) bieten dabei stets beide möglichen Zustände des Speicherelements, was die Flexibilität in der Schaltungsgestaltung erhöht und die Notwendigkeit weiterer Inverter reduziert.

Anwendungsbereiche und Implementierung

Der MOS 4027 ist ein universelles Bauteil in der digitalen Elektronik und findet Anwendung in einer Vielzahl von Projekten:

- Zähler und Frequenzteiler: Durch Kaskadierung mehrerer MOS 4027 können einfache Binärzähler oder präzise Frequenzteiler für Taktsignale realisiert werden.

- Schieberegister: Speicherung und sequenzielle Übertragung von Datenbits, essenziell für serielle Datenkommunikation oder Datenspeicherung.

- Zustandsautomaten: Aufbau von einfachen Steuerungslogiken, die auf eine Abfolge von Eingaben reagieren.

- Speicherelemente: Als grundlegender Baustein zur Speicherung eines einzelnen Bits in komplexeren Speicherschaltungen.

- Taktverteilung und Synchronisation: Zur Steuerung von Timing-Signalen in komplexen digitalen Systemen, um sicherzustellen, dass alle Operationen im richtigen Moment erfolgen.

- Lern- und Hobbyprojekte: Ideal für Studenten und Elektronikenthusiasten, um die Grundlagen der digitalen Logik und des Schaltungsdesigns zu erlernen und anzuwenden.

Die DIP-16-Bauform macht den MOS 4027 besonders zugänglich für den Einsatz auf Prototypenplatinen (Breadboards) und für manuelles Löten. Die breite Betriebsspannung von 3 V bis 15 V ermöglicht die Integration in Projekte mit unterschiedlichsten Stromversorgungen, von energiesparenden Mikrocontroller-basierten Systemen bis hin zu Robotersteuerungen oder industriellen Automatisierungskomponenten.

FAQ – Häufig gestellte Fragen zu MOS 4027 – Flip-Flop JK-Type, Dual, 3 … 15 V, DIP-16

Was genau ist ein JK-Flip-Flop und wie unterscheidet er sich von einem D-Flip-Flop?

Ein JK-Flip-Flop ist ein digitaler Speicherbaustein, der zwei stabile Zustände (0 oder 1) halten kann. Er unterscheidet sich von einem D-Flip-Flop (Data-Flip-Flop) hauptsächlich durch seine komplexere Steuerlogik. Während ein D-Flip-Flop den Zustand des Ausgangs direkt durch seinen D-Eingang bestimmt, der bei jeder Taktflanke übernommen wird, bietet ein JK-Flip-Flop mehr Flexibilität. Seine J- und K-Eingänge erlauben eine Vielzahl von Operationen: Speichern des aktuellen Zustands (wenn J=0, K=0), Setzen auf 1 (wenn J=1, K=0), Zurücksetzen auf 0 (wenn J=0, K=1) und Toggle (Umschalten des Zustands, wenn J=1, K=1). Diese Toggle-Funktion ist entscheidend für Zähler und Frequenzteiler.

Welche Vorteile bietet die CMOS-Technologie des MOS 4027?

Die CMOS-Technologie (Complementary Metal-Oxide-Semiconductor) bietet mehrere signifikante Vorteile. Erstens zeichnet sie sich durch einen sehr geringen Stromverbrauch aus, insbesondere im statischen Zustand, was ihn ideal für batteriebetriebene Anwendungen macht. Zweitens bietet CMOS eine hohe Störfestigkeit gegenüber elektrischem Rauschen, was die Zuverlässigkeit von Schaltungen erhöht. Drittens ist die hohe Schaltgeschwindigkeit bei gleichzeitig geringer Leistungsaufnahme charakteristisch für CMOS.

Ist der MOS 4027 für Anfänger im Elektronikbereich geeignet?

Ja, der MOS 4027 ist aufgrund seiner bewährten Funktionsweise, der klaren Spezifikationen und der einfachen Integration (insbesondere im DIP-16-Gehäuse) hervorragend für Lernprojekte geeignet. Er ermöglicht das praktische Verständnis grundlegender digitaler Logikkonzepte wie Speicherung, Zustandswechsel und Taktsteuerung.

Welche Bedeutung hat der breite Betriebsspannungsbereich von 3 V bis 15 V?

Der weite Betriebsspannungsbereich des MOS 4027 bietet erhebliche Flexibilität. Er ermöglicht die Verwendung des ICs in einer Vielzahl von Systemen, von Niederspannungsanwendungen (z.B. mit 3.3V oder 5V Mikrocontrollern) bis hin zu Systemen, die höhere Spannungen erfordern. Diese Anpassungsfähigkeit vereinfacht die Integration in bestehende oder neu entwickelte Schaltungen, ohne dass zusätzliche Spannungsregulatoren notwendig sind, solange die Systemspannung innerhalb des spezifizierten Bereichs liegt.

Was bedeutet „Dual“ im Zusammenhang mit diesem Flip-Flop?

„Dual“ bedeutet, dass der MOS 4027 integrierte Schaltkreis zwei vollständige und voneinander unabhängige JK-Flip-Flops in einem einzigen Gehäuse vereint. Jeder dieser Flip-Flops verfügt über seine eigenen J-, K-, Set-, Reset- und Clock-Eingänge sowie seine eigenen Q- und Q-nicht-Ausgänge. Dies ermöglicht die gleichzeitige Realisierung von zwei unterschiedlichen Speicher- oder Steuerfunktionen mit nur einem IC, was Platz und Kosten spart.

Können die Set- und Reset-Eingänge verwendet werden, um die Flip-Flops zu synchronisieren?

Die Set- (S) und Reset- (R) Eingänge des MOS 4027 sind asynchron. Das bedeutet, sie wirken unabhängig vom Taktsignal. Sie werden verwendet, um den Ausgang (Q) sofort auf einen bestimmten Zustand zu setzen (S=HIGH) oder zurückzusetzen (R=HIGH), ohne auf die nächste Taktflanke warten zu müssen. Dies ist ideal für die Initialisierung des Systems oder das Erzwingen eines bekannten Anfangszustands, aber sie sind nicht Teil des synchronen Betriebsmechanismus für den normalen Datenwechsel.

Wie wird die Taktflankensteuerung (Edge Triggering) beim MOS 4027 implementiert?

Der MOS 4027 ist ein „Edge-Triggered“ Flip-Flop. Das bedeutet, dass die Zustandsänderung des Ausgangs (Q) nur zum Zeitpunkt einer bestimmten Taktflanke stattfindet – entweder zur steigenden (LOW zu HIGH) oder zur fallenden (HIGH zu LOW) Flanke des Clock-Signals, je nach spezifischem Design des ICs. Dies sorgt für eine präzise und deterministische Synchronisation von Daten mit dem Taktgeber und ist entscheidend für die Vermeidung von Timing-Problemen und Race Conditions in digitalen Systemen.