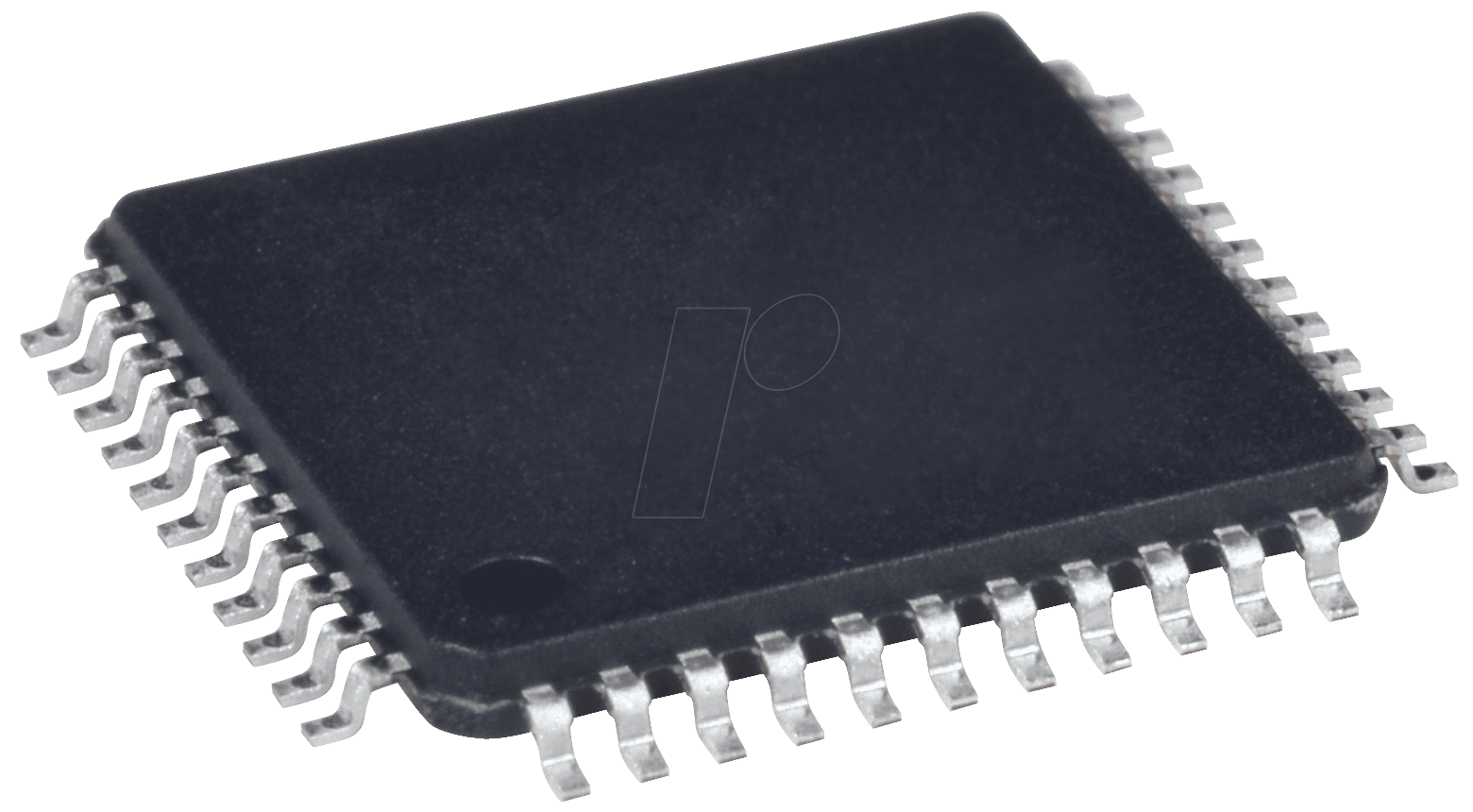

Optimierte digitale Logik mit dem M4A5 64/32-10 VC – CPLD ispMACH

Für Ingenieure und Entwickler, die komplexe digitale Schaltungen mit hoher Effizienz und Flexibilität realisieren müssen, bietet das M4A5 64/32-10 VC – CPLD ispMACH die ideale Lösung. Dieses programmierbare Logikbaustein ermöglicht die Gestaltung und Implementierung maßgeschneiderter Funktionen, die weit über die Möglichkeiten diskreter Logikgatter hinausgehen und dabei eine signifikante Reduktion der Bauteilanzahl und des Platzbedarfs bewirken.

Leistungsstarke Funktionalität für anspruchsvolle Applikationen

Das M4A5 64/32-10 VC – CPLD ispMACH zeichnet sich durch seine leistungsstarke Architektur aus, die eine schnelle und zuverlässige Verarbeitung digitaler Signale gewährleistet. Mit 64 Makrozellen und einer Gate-Äquivalenz von 2550 Gates bietet es ausreichend Ressourcen für eine breite Palette von Anwendungen, von der Steuerung komplexer Systeme bis hin zur Signalverarbeitung und Datenmanipulation. Die 5 V Betriebsspannung macht es zudem kompatibel mit vielen bestehenden Systemen und vereinfacht die Integration.

Überlegene Vorteile gegenüber Standardlösungen

- Hohe Flexibilität und Anpassungsfähigkeit: Im Gegensatz zu ASICs, die fest verdrahtet sind, ermöglicht die programmierbare Natur des CPLD eine einfache Modifikation der Logikfunktionen, auch nach der Fertigung des Endprodukts. Dies spart Entwicklungszeit und -kosten bei sich ändernden Anforderungen.

- Kompakter Formfaktor und erhöhte Systemintegration: Das TQFP-44 Gehäuse bietet eine platzsparende Lösung, die es Entwicklern ermöglicht, hochintegrierte und kompakte Designs zu realisieren. Dies ist entscheidend für Anwendungen mit begrenztem Bauraum.

- Reduktion der Stücklistenkosten (BOM): Durch die Integration mehrerer Logikfunktionen in einem einzigen Baustein können die Gesamtkosten für die Stückliste erheblich gesenkt werden, da weniger einzelne Komponenten benötigt werden.

- Verbesserte Signalintegrität und Performance: Die optimierte interne Architektur und die kurze Signalpfadlänge innerhalb des CPLD führen zu einer verbesserten Signalintegrität und höheren Schaltgeschwindigkeiten im Vergleich zu diskreten Logiklösungen.

- Energieeffizienz im Betrieb: Während die 5 V Betriebsspannung eine breite Kompatibilität sicherstellt, bietet die ispMACH-Architektur einen optimierten Energieverbrauch für die jeweilige Funktionalität, was in vielen Anwendungen von Vorteil ist.

- Einfache Entwicklungsumgebung und In-System-Programmierbarkeit (ISP): Die ispMACH-Technologie ermöglicht die Programmierung des CPLD direkt auf der Platine, was den Entwicklungs- und Testprozess erheblich beschleunigt und vereinfacht.

Technische Spezifikationen im Detail

| Merkmal | Spezifikation | Vorteil für den Anwender |

|---|---|---|

| Bausteintyp | CPLD (Complex Programmable Logic Device) | Bietet hohe Flexibilität bei der Implementierung komplexer digitaler Logikfunktionen. |

| Makrozellen | 64 | Ermöglicht die Realisierung einer signifikanten Anzahl von Logikfunktionen und State Machines. |

| Gate-Äquivalenz | 2550 | Stellt ausreichende Kapazitäten für anspruchsvolle digitale Schaltungsdesigns bereit. |

| Betriebsspannung | 5 V | Kompatibel mit einer Vielzahl von digitalen Systemen und einfachen Stromversorgungen. |

| Gehäusetyp | TQFP-44 | Kompakter und montagefreundlicher Oberflächenmontagebaustein, ideal für platzkritische Designs. |

| Programmiertechnologie | ispMACH (In-System Programmable) | Ermöglicht die Aktualisierung der Firmware und Anpassung der Logik direkt auf der Zielplatine, was den Entwicklungsprozess beschleunigt. |

| Anwendungsbereiche | Universelle Logikfunktionen, Mikrocontroller-Peripherie, Signalaufbereitung, Zustandsautomaten, Schnittstellen-Logik. | Vielseitig einsetzbar in einer breiten Palette von Embedded-Systemen und elektronischen Geräten. |

| Schaltgeschwindigkeit | Optimierte interne Pfadlängen für schnelle Logikoperationen. | Gewährleistet schnelle Reaktionszeiten und hohe Systemperformance. |

Detaillierte Anwendungsbereiche und Designaspekte

Das M4A5 64/32-10 VC – CPLD ispMACH ist ein Eckpfeiler für Entwickler, die ihre Designs auf die nächste Stufe heben möchten. Die 64 Makrozellen bieten einen beträchtlichen Spielraum für die Implementierung von komplexen Zustandsautomaten, die für die Steuerung von Prozessen in industriellen Automatisierungssystemen oder Robotik unerlässlich sind. Darüber hinaus kann die hohe Gate-Äquivalenz von 2550 Gates genutzt werden, um umfangreiche Datenauswertungen oder benutzerdefinierte Schnittstellen zu realisieren, beispielsweise zur Anbindung von Sensoren oder Aktoren an einen Mikrocontroller. Die 5 V Betriebsspannung ist ein klares Plus für Projekte, die auf etablierten und weit verbreiteten Stromversorgungstechnologien basieren, und vereinfacht die Kompatibilität mit älteren oder weniger modernen Systemkomponenten. Die in-system programmierbare Funktionalität der ispMACH-Technologie reduziert den Aufwand für Iterationen und Tests erheblich. Entwickler können das Design direkt auf der Leiterplatte ändern und neu programmieren, ohne den Baustein auslöten zu müssen. Dies beschleunigt den Prototyping-Zyklus und ermöglicht eine schnellere Markteinführung. Die Wahl des TQFP-44 Gehäuses unterstreicht die Ausrichtung auf kompakte und ästhetisch anspruchsvolle elektronische Geräte, bei denen der Platz auf der Platine eine kritische Ressource darstellt. Von tragbaren Messgeräten bis hin zu komplexen Kommunikationsmodulen – die geringe Bauhöhe und der standardisierte Footprint erleichtern die Integration in vielfältige Gehäusekonzepte.

Die semantische Stärke dieses CPLDs liegt in seiner Fähigkeit, als hochspezialisierter „digitaler Klebstoff“ zu fungieren, der verschiedene Funktionseinheiten eines Systems miteinander verbindet und deren Zusammenspiel optimiert. Anstelle vieler kleinerer Logikchips kann ein einziges M4A5 64/32-10 VC – CPLD die Funktionalität mehrerer Bauteile übernehmen, was zu einer drastischen Reduzierung der Komplexität des Leiterplattendesigns, der Montage und der Fehlersuche führt. Dies ist insbesondere in der Embedded-System-Entwicklung, wo Ressourcen oft knapp sind, von unschätzbarem Wert.

FAQ – Häufig gestellte Fragen zu M4A5 64/32-10 VC – CPLD ispMACH, 64 Makrozellen, 2550 Gate, 5 V, TQFP-44

Was ist ein CPLD und wie unterscheidet es sich von einem FPGA?

Ein CPLD (Complex Programmable Logic Device) ist ein programmierbarer Logikbaustein, der aus einer größeren Anzahl von Logikelementen besteht als ein einfacherer PLD. Im Gegensatz zu FPGAs (Field-Programmable Gate Arrays), die eine flexiblere Routing-Architektur und eine größere Anzahl von Logikzellen aufweisen, sind CPLDs oft für kleinere bis mittlere Designs optimiert, die eine nicht-flüchtige Speicherung der Konfiguration erfordern. Die ispMACH-Architektur des M4A5 64/32-10 VC – CPLD bietet im Vergleich zu manchen älteren CPLD-Technologien eine verbesserte Performance und einfachere In-System-Programmierung.

Welche Vorteile bietet die 5 V Betriebsspannung?

Die 5 V Betriebsspannung gewährleistet eine hohe Kompatibilität mit vielen etablierten digitalen Logikfamilien und Stromversorgungssystemen. Dies erleichtert die Integration in bestehende Designs oder die Verwendung mit Standard-Spannungsreglern, was die Entwicklung vereinfacht und Kosten spart.

Ist das M4A5 64/32-10 VC – CPLD ispMACH für Anfänger geeignet?

Das M4A5 64/32-10 VC – CPLD ispMACH ist primär für professionelle Ingenieure und Entwickler konzipiert, die Erfahrung mit digitaler Logik und der Verwendung von programmierbaren Logikbausteinen haben. Die Entwicklung erfordert Kenntnisse in Hardware-Beschreibungssprachen (wie VHDL oder Verilog) und die Bedienung spezifischer Entwicklungswerkzeuge.

Wie wird das CPLD programmiert?

Die Programmierung des M4A5 64/32-10 VC – CPLD ispMACH erfolgt mittels In-System-Programmierung (ISP) über eine dedizierte Schnittstelle, die typischerweise JTAG oder eine serielle Schnittstelle verwendet. Dies geschieht in der Regel mit spezieller Software und einem Programmieradapter, während sich der Baustein bereits auf der Zielplatine befindet.

Welche Arten von Logikfunktionen können mit 64 Makrozellen realisiert werden?

Mit 64 Makrozellen lassen sich eine Vielzahl von Logikfunktionen realisieren, darunter komplexe kombinatorische Logik, bis zu etwa 32-Bit breite Zähler oder Register, und diverse Zustandsautomaten mit einer moderaten Anzahl von Zuständen. Die genaue Anzahl hängt von der Komplexität der einzelnen Funktionen ab.

Unterstützt dieses CPLD niedrige Stromverbrauchsmodi?

Die ispMACH-Architektur ist auf eine effiziente Nutzung der Ressourcen ausgelegt. Während spezifische Low-Power-Modi von der Implementierung abhängen, bietet die Natur eines CPLD im Vergleich zu nicht-programmierbaren Lösungen oft eine gute Balance zwischen Leistung und Energieverbrauch für die jeweilige Funktion.

Welche Software wird für die Entwicklung mit diesem CPLD benötigt?

Für die Entwicklung mit ispMACH CPLDs werden typischerweise die entsprechenden Design-Suites des Herstellers benötigt, die Software zur Logiksynthese, Place & Route, Simulation und zur Erzeugung der Programmierdateien (JEDEC-Files) umfassen. Diese Tools sind unerlässlich, um die gewünschte Logik zu definieren und auf den Baustein zu übertragen.