Maximale Flexibilität und Performance für komplexe digitale Schaltungen: M4A5 32/32-10 VC ispMACH 4A CPLDs

Das M4A5 32/32-10 VC aus der ispMACH 4A Familie von Lattice Semiconductor ist die ideale Lösung für Ingenieure und Entwickler, die eine leistungsstarke und gleichzeitig energieeffiziente Alternative für anspruchsvolle Logikimplementierungen suchen. Dieses CPLD bietet 32 Makrozellen und ist für eine Betriebsspannung von 5V ausgelegt, was es zur perfekten Wahl für viele bestehende und neue Design-Anforderungen im Bereich der digitalen Signalverarbeitung und Steuerungselektronik macht.

Leistungsmerkmale und Design-Vorteile

Das ispMACH 4A CPLD-Portfolio zeichnet sich durch eine Kombination aus hoher Performance, geringem Stromverbrauch und flexiblen I/O-Optionen aus. Das M4A5 32/32-10 VC, mit seinen 32 dedizierten Makrozellen, ermöglicht die Implementierung komplexer Funktionen auf engstem Raum. Die Architektur ist auf maximale Flexibilität ausgelegt, sodass Designs schnell angepasst und optimiert werden können. Dies unterscheidet es signifikant von starreren FPGA-Lösungen oder festverdrahteten ASICs, bei denen Designänderungen kostspielig und zeitaufwändig sind.

- Hohe Integrationsdichte: Mit 32 Makrozellen können Sie komplexe Logikfunktionen effizient auf einem einzigen Baustein abbilden, was zu einer Reduzierung der Stückzahl und des Platzbedarfs auf der Platine führt.

- 5V Betriebsspannungskompatibilität: Die Kompatibilität mit 5V-Systemen erleichtert die Integration in bestehende Hardware-Designs, ohne aufwändige Pegelwandler oder zusätzliche Spannungsregler.

- Schnelle Programmierbarkeit und In-System-Konfiguration: Die ispMACH 4A-Familie unterstützt die In-System-Programmierbarkeit (ISP), was schnelle Iterationen während des Entwicklungsprozesses und einfache Updates im Feld ermöglicht.

- Optimierte Leistung für Echtzeitanwendungen: Die dedizierte Makrozellen-Architektur und die schnelle Routing-Matrix sorgen für vorhersagbare Timing-Charakteristiken, die für Echtzeitanwendungen unerlässlich sind.

- Geringer Stromverbrauch: Trotz der hohen Leistung ist die ispMACH 4A-Familie für ihren vergleichsweise geringen Stromverbrauch bekannt, was besonders in batteriebetriebenen oder energiebewussten Anwendungen von Vorteil ist.

Architektur und Technologie im Detail

Die ispMACH 4A CPLDs basieren auf einer nicht-flüchtigen Flash-Technologie, die eine schnelle und zuverlässige Konfiguration ermöglicht. Jede Makrozelle ist mit einem flexiblen Produktterm-Array (PTA) ausgestattet, das eine Vielzahl von Logikfunktionen realisieren kann. Die Architektur verfügt über eine hochleistungsfähige interconnect Matrix, die eine schnelle Signalweiterleitung zwischen den Makrozellen und den I/O-Pins gewährleistet. Dies minimiert die Signalverzögerung und ermöglicht die Implementierung von Designs mit hohen Taktfrequenzen.

Im Gegensatz zu traditionellen PLDs mit weniger komplexen Architekturen bietet das M4A5 32/32-10 VC durch seine Makrozellen mit größeren Produktterm-Kapazitäten eine höhere Funktionalität pro Zelle. Dies reduziert die Notwendigkeit, Designs auf mehrere kleinere Logikbausteine aufzuteilen, was zu einer Vereinfachung der Leiterplattenlayouts und einer potenziellen Reduzierung von Signalinterferenzen führt.

Anwendungsbereiche und Implementierungsbeispiele

Das M4A5 32/32-10 VC ist ein vielseitiger Baustein, der in einer breiten Palette von Anwendungen eingesetzt werden kann:

- Universelle Logikfunktionen: Realisierung von kombinatorischer und sequentieller Logik, wie z.B. Decodern, Multiplexern, Zählern oder Zustandsautomaten.

- Schnittstellenlogik: Ansteuerung von Peripheriegeräten, Pufferung von Signalen oder Implementierung von Protokollkonvertern.

- Controller für kleinere Systeme: Steuerung von Motoren, Anzeigen oder einfachen industriellen Prozessen.

- Erweiterung von Mikrocontroller-Systemen: Bereitstellung zusätzlicher I/O-Ports oder Implementierung von spezialisierten Steuerungsfunktionen, die über die Fähigkeiten eines Mikrocontrollers hinausgehen.

- Prototyping und F&E: Schnelle und kostengünstige Erprobung neuer Logikkonzepte und Hardware-Designs.

Die 5V-Betriebsspannung macht diesen CPLD besonders attraktiv für die Nachrüstung bestehender Systeme, die auf älteren 5V-Logikfamilien basieren, wie z.B. TTL (Transistor-Transistor-Logik) oder ältere CMOS-Technologien. Dies ermöglicht eine reibungslose Integration und spart erhebliche Kosten für die Umgestaltung ganzer Platinen.

Produkteigenschaften im Überblick

| Merkmal | Beschreibung |

|---|---|

| Produktfamilie | ispMACH 4A |

| Modell | M4A5 32/32-10 VC |

| Logikzellen | 32 Makrozellen |

| Betriebsspannung | 5 V |

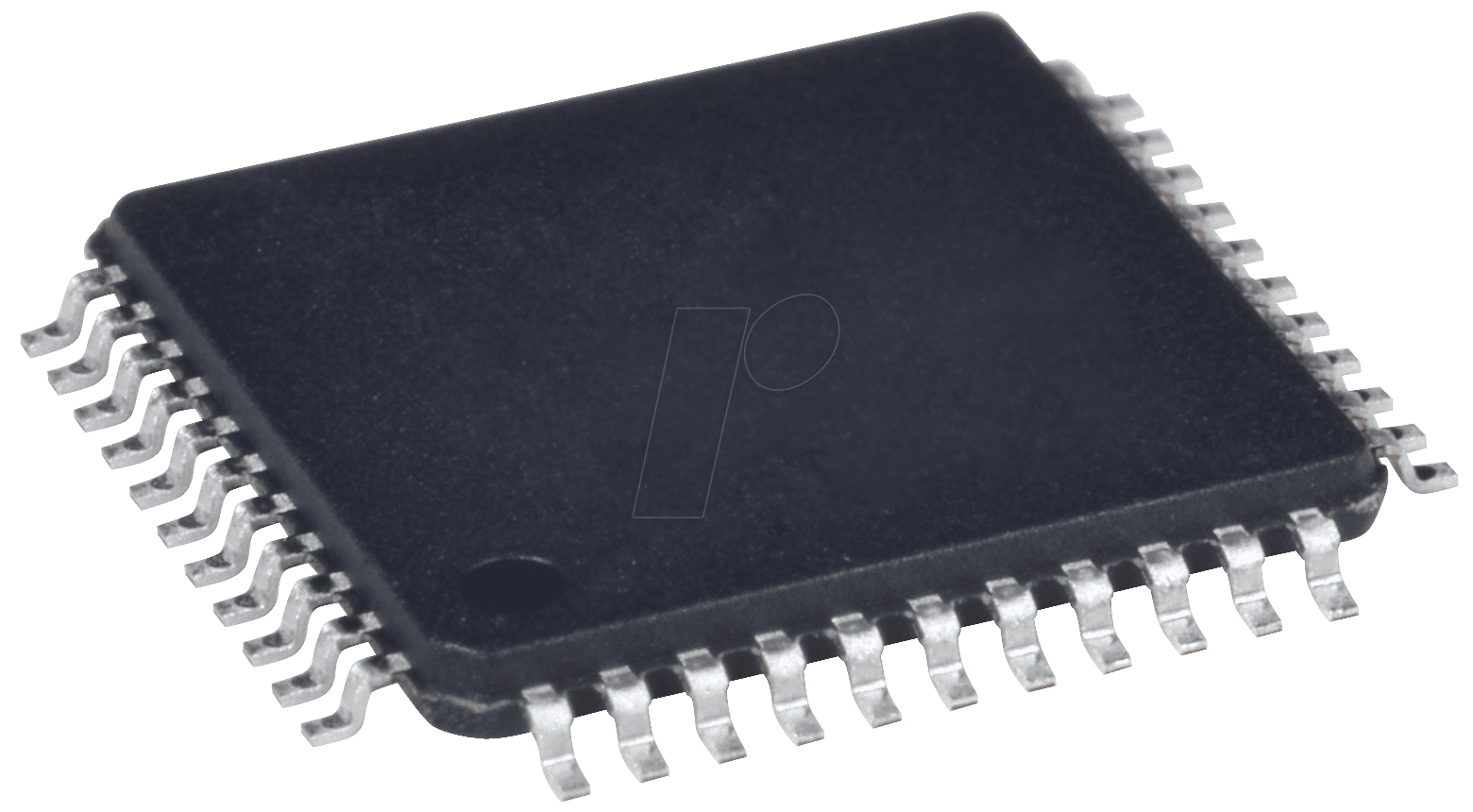

| Gehäusetyp | TQFP-44 |

| Programmiertechnologie | Nicht-flüchtiger Flash-Speicher |

| I/O-Standard-Kompatibilität | Unterstützt verschiedene I/O-Standards, typischerweise 3.3V und 5V Logikkompatibilität durch Konfiguration der I/O-Banking-Funktionen. (Spezifische Details im Datenblatt) |

| Entwicklungsunterstützung | Unterstützt durch Lattice’s ISPtools und gängige HDL-Synthese-Tools. |

Häufig gestellte Fragen zu M4A5 32/32-10 VC – ispMACH 4A CPLDs, 32 Makrozellen, 5 V, TQFP-44

Was bedeutet „Makrozelle“ im Kontext von CPLDs?

Eine Makrozelle ist die grundlegende Logikeinheit eines Complex Programmable Logic Device (CPLD). Sie besteht typischerweise aus einem Programmierbaren Produktterm-Array (PTA) und einer Regal- oder D-Flipflop-Einheit. Die Makrozelle kann so konfiguriert werden, dass sie eine breite Palette von kombinatorischer und sequentieller Logik implementiert. Die Anzahl der Makrozellen gibt die Größe und Komplexität der Logik an, die in dem Chip untergebracht werden kann.

Warum ist die 5V-Betriebsspannung von Vorteil?

Die 5V-Betriebsspannung ist von großem Vorteil, da sie eine direkte Kompatibilität mit vielen älteren und bestehenden digitalen Systemen ermöglicht, die auf 5V-Logikfamilien wie TTL oder älteren CMOS-Standards basieren. Dies vereinfacht die Integration in bestehende Designs erheblich, da keine Pegelwandler oder komplexen Spannungsregulierungen erforderlich sind, was Kosten und Entwicklungsaufwand reduziert.

Wie unterscheidet sich ein CPLD von einem FPGA?

Der Hauptunterschied liegt in der Architektur und der Nicht-Flüchtigkeit. CPLDs, wie die ispMACH 4A-Familie, verwenden eine nicht-flüchtige Speichertechnologie (Flash) und haben eine gleichmäßigere, Produktterm-basierte Logikstruktur. Dies führt zu einer vorhersagbareren Leistung und einer schnellen Einschaltzeit. FPGAs (Field-Programmable Gate Arrays) verwenden typischerweise SRAM-basierte Konfiguration, was mehr Flexibilität bei der Logikzuweisung und größere Kapazitäten bietet, aber eine externe Konfigurationsspeicherquelle benötigt und langsamere Einschaltzeiten hat.

Welche Art von Software wird für die Programmierung dieses CPLDs benötigt?

Für die Programmierung und Konfiguration von ispMACH 4A CPLDs wird in der Regel die Entwicklungssoftware von Lattice Semiconductor benötigt, wie z.B. die ispLEVER-Software oder neuere Versionen davon. Diese Tools ermöglichen das Design mit Hardware Description Languages (HDLs) wie VHDL oder Verilog, die Synthese, die Platzierung und das Routing sowie die Generierung der Konfigurationsdatei (JEDEC-Datei), die dann auf den Chip geladen wird.

Ist das M4A5 32/32-10 VC für Hochfrequenzanwendungen geeignet?

Ja, die ispMACH 4A CPLDs sind für ihre schnelle und vorhersagbare Leistung bekannt, die sie für viele Hochfrequenzanwendungen geeignet macht. Die dedizierte Logikarchitektur und die optimierte interconnect Matrix minimieren Signallaufzeiten, was für Anwendungen mit hohen Taktfrequenzen entscheidend ist. Die genauen Hochfrequenzfähigkeiten hängen vom spezifischen Design und den Timing-Anforderungen ab und sollten anhand des Datenblatts und der Simulationsergebnisse bewertet werden.

Wie kann die „In-System-Programmierbarkeit“ (ISP) genutzt werden?

Die In-System-Programmierbarkeit (ISP) ermöglicht es, das CPLD direkt auf der Leiterplatte zu programmieren, nachdem es montiert wurde. Dies ist ein erheblicher Vorteil für die Entwicklung und Produktion. Während der Entwicklung erlaubt ISP schnelle Iterationen, da das Design auf der Platine getestet und sofort aktualisiert werden kann. In der Produktion vereinfacht es den Fertigungsprozess. Nach der Auslieferung können Produkte auch im Feld aktualisiert werden, falls eine neue Firmware-Version oder eine Fehlerkorrektur erforderlich ist.

Welche Vorteile bietet der TQFP-44 Gehäusetyp?

Der TQFP (Thin Quad Flat Pack)-44 ist ein gängiger oberflächenmontierbarer Gehäusetyp, der eine gute Balance zwischen Pin-Dichte und Handhabbarkeit bietet. Er ist relativ klein, was ihn für Designs mit begrenztem Platz auf der Leiterplatte gut geeignet macht. Die 44 Pins bieten genügend Anschlüsse für die 32 Makrozellen und die notwendigen I/O-Ports, was eine flexible Anbindung an das System ermöglicht, ohne übermäßig viel Platz auf der Platine zu beanspruchen. Dies erleichtert auch die automatische Bestückung.