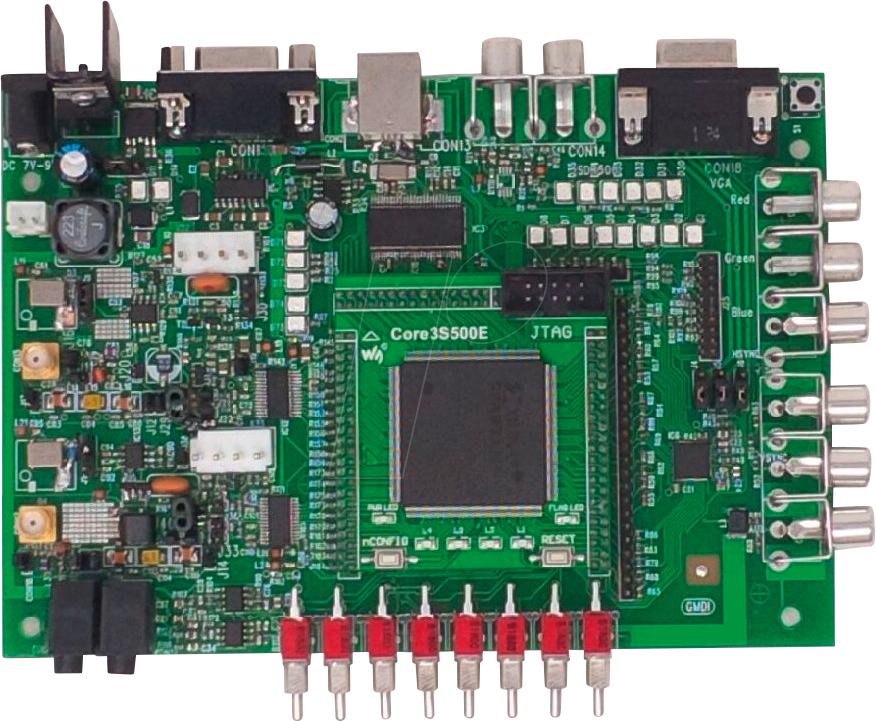

Revolutionieren Sie Ihre Signalverarbeitung mit dem HUSP E3050 – SDR-500 FPGA-Evalboard

Das HUSP E3050 – SDR-500 High-Speed Digital Signal Processing FPGA-Evalboard wurde speziell für Ingenieure, Forscher und Entwickler entwickelt, die anspruchsvolle digitale Signalverarbeitungsaufgaben mit höchster Geschwindigkeit und Präzision bewältigen müssen. Wenn Sie nach einer leistungsstarken Plattform suchen, um komplexe Algorithmen zu implementieren, neue SDR-Architekturen zu testen oder Echtzeitdatenströme zu analysieren, bietet dieses Evalboard eine überlegene Alternative zu herkömmlichen, fest verdrahteten oder weniger flexiblen Verarbeitungssystemen.

Leistung und Flexibilität für höchste Ansprüche

Das Herzstück des HUSP E3050 bildet ein hochmoderner FPGA (Field-Programmable Gate Array), der eine beispiellose programmierbare Logik und Parallelverarbeitung ermöglicht. Dies unterscheidet es fundamental von standardmäßigen CPUs oder spezialisierten DSPs, die oft durch ihre feste Architektur limitiert sind. Mit dem HUSP E3050 können Sie Ihre Signalverarbeitungsketten maßschneidern, Algorithmen direkt in Hardware beschleunigen und somit Latenzzeiten drastisch reduzieren und den Datendurchsatz maximieren. Die hohe Flexibilität erlaubt es Ihnen, sich schnell an neue Anforderungen anzupassen und innovative Lösungen zu entwickeln, ohne auf teure kundenspezifische Hardwareentwicklungen warten zu müssen.

Herausragende Merkmale des HUSP E3050 – SDR-500

- Hochleistungs-FPGA-Architektur: Ermöglicht komplexe parallele Verarbeitungsaufgaben und hardwarebeschleunigte Algorithmen.

- Flexible Konfigurierbarkeit: Passen Sie die Hardware-Logik präzise an Ihre spezifischen Anwendungsanforderungen an.

- Optimiert für High-Speed-SDR-Anwendungen: Ideal für Software-Defined Radio, Telekommunikation und anspruchsvolle Echtzeit-Signalverarbeitung.

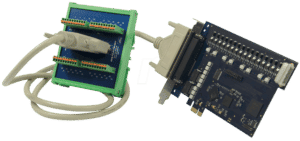

- Umfassende Schnittstellen: Bietet eine breite Palette von Konnektivitätsoptionen für externe Komponenten und Datenerfassung.

- Entwicklerfreundliches Ökosystem: Unterstützt gängige Entwicklungstools und Programmiersprachen für eine effiziente Implementierung.

- Reduzierte Latenzzeiten: Direkte Hardware-Implementierung von Algorithmen minimiert Verarbeitungsverzögerungen.

- Hoher Datendurchsatz: Bewältigen Sie selbst die anspruchsvollsten Datenströme mit Leichtigkeit.

Anwendungsbereiche und Potenzial

Das HUSP E3050 – SDR-500 Evalboard eröffnet neue Horizonte in einer Vielzahl von technischen Domänen. Im Bereich der Software-Defined Radio (SDR) ermöglicht es die Implementierung komplexer Modulations- und Demodulationsschemata, die Filterung von Rauschen in Echtzeit und die adaptive Anpassung von Funkparametern. Dies ist essenziell für fortschrittliche Kommunikationssysteme, Radarapplikationen und elektronische Kriegsführung. In der industriellen Automatisierung und Robotik kann es zur schnellen Verarbeitung von Sensorikdaten, zur präzisen Steuerung von Motoren und zur Implementierung von maschinellem Sehen in Echtzeit genutzt werden. Für wissenschaftliche Forschung und Prototyping ist es eine unverzichtbare Plattform zur Untersuchung neuartiger Signalverarbeitungsalgorithmen, zur Datenanalyse in Hochenergiephysikexperimenten oder zur Entwicklung spezialisierter Messtechnik. Auch in der Medizintechnik findet es Anwendung, beispielsweise bei der Echtzeit-Bildverarbeitung für diagnostische Geräte oder der Signalverarbeitung von biometrischen Daten.

Technische Spezifikationen im Detail

| Merkmal | Spezifikation / Beschreibung |

|---|---|

| FPGA-Typ | Hochleistungs-FPGA mit optimierter Logik für parallele Signalverarbeitung |

| Verarbeitungsgeschwindigkeit | Entwickelt für Taktfrequenzen im hohen MHz- bis niedrigen GHz-Bereich, abhängig von der Implementierung und Konfiguration. Ermöglicht signifikant höhere Verarbeitungsraten als vergleichbare CPU-basierte Lösungen. |

| Speicherinterface | Unterstützung für schnelle Speicherinterfaces zur Bewältigung großer Datensätze und zur effizienten Zwischenspeicherung von Signalverarbeitungsdaten. |

| I/O-Schnittstellen | Vielfältige Hochgeschwindigkeitsschnittstellen für die Anbindung von ADCs/DACs, externen Speicherbausteinen und Peripheriegeräten. |

| Entwicklungssoftware | Kompatibilität mit etablierten FPGA-Entwicklungsumgebungen (z.B. VHDL, Verilog) und Simulierungswerkzeugen, um eine reibungslose Entwicklung zu gewährleisten. |

| Stromversorgung | Standardisierte Stromversorgungsanforderungen für einfache Integration in bestehende Testaufbauten. Detaillierte Angaben sind im technischen Datenblatt verfügbar. |

| Formfaktor | Kompaktes Evalboard-Design, optimiert für den Einsatz auf Labortischen und in Prototypen. |

| Konfiguration | Konfigurierbar über JTAG-Schnittstelle für schnelle Iterationen und Debugging. |

Warum das HUSP E3050 – SDR-500 Ihre erste Wahl sein sollte

Im Vergleich zu herkömmlichen Prozessoren, die oft sequenziell arbeiten und bei komplexen Signalverarbeitungsaufgaben an ihre Grenzen stoßen, bietet das HUSP E3050 – SDR-500 die inhärente Parallelität und Flexibilität von FPGAs. Dies ermöglicht eine drastische Beschleunigung von rechenintensiven Algorithmen, was insbesondere in zeitkritischen Anwendungen wie SDR von unschätzbarem Wert ist. Anstatt auf Software-Updates für neue Funktionalitäten warten zu müssen, können Sie mit diesem Evalboard direkt die Hardware entsprechend Ihrer neuesten Entwürfe und Anforderungen umprogrammieren. Die Fähigkeit, Signalverarbeitungsfunktionen auf Hardware-Ebene zu implementieren, minimiert Latenzzeiten und maximiert den Durchsatz, was bei der Verarbeitung großer Datenmengen in Echtzeit einen entscheidenden Vorteil darstellt. Das HUSP E3050 ist somit nicht nur ein Entwicklungswerkzeug, sondern eine strategische Investition in zukunftsfähige und leistungsstarke Signalverarbeitungslösungen.

FAQ – Häufig gestellte Fragen zu HUSP E3050 – SDR-500 High-Speed Digital Signal Processing FPGA-Evalboard

Ist das HUSP E3050 – SDR-500 für Anfänger geeignet?

Das HUSP E3050 – SDR-500 ist primär für erfahrene Ingenieure und Entwickler konzipiert, die bereits Kenntnisse in digitaler Signalverarbeitung und FPGA-Programmierung (z.B. VHDL oder Verilog) besitzen. Die Komplexität und Leistungsfähigkeit erfordern ein fundiertes technisches Verständnis.

Welche Entwicklungsumgebungen werden unterstützt?

Das Evalboard ist mit den gängigen FPGA-Entwicklungsumgebungen der führenden Hersteller kompatibel. Detaillierte Informationen zu spezifischen Softwarepaketen und Treiberunterstützung finden Sie im zugehörigen technischen Datenblatt und der Dokumentation.

Kann ich eigene Algorithmen auf dem HUSP E3050 implementieren?

Ja, die programmierbare Natur des FPGAs ermöglicht die Implementierung und Optimierung nahezu aller digitalen Signalverarbeitungsalgorithmen. Sie haben die volle Kontrolle über die Hardware-Logik.

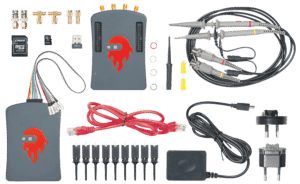

Welche Art von Schnittstellen sind verfügbar, um externe Komponenten anzuschließen?

Das Board verfügt über eine Vielzahl von Hochgeschwindigkeitsschnittstellen, die für die Anbindung von Analog-Digital-Wandlern (ADCs), Digital-Analog-Wandlern (DACs), Speicher und anderen externen Peripheriegeräten ausgelegt sind. Die genauen Schnittstellen sind im technischen Datenblatt aufgeführt.

Wie unterscheidet sich dieses Evalboard von einer reinen DSP-Platine?

Während spezialisierte DSPs optimiert sind für bestimmte mathematische Operationen, bietet ein FPGA wie im HUSP E3050 eine deutlich höhere Flexibilität und Parallelität. Sie können Ihre Signalverarbeitungsketten komplett neu definieren und an Ihre spezifischen Bedürfnisse anpassen, was bei fest verdrahteten DSPs nicht möglich ist.

Ist das HUSP E3050 – SDR-500 für kommerzielle Produkte geeignet?

Dieses Evalboard ist in erster Linie für Prototyping, Forschung und Entwicklung gedacht. Für kommerzielle Produkte empfehlen wir, auf Basis der Erkenntnisse und Designs, die mit diesem Evalboard entwickelt wurden, eine dedizierte ASIC- oder FPGA-basierte Lösung zu entwickeln oder ein entsprechendes Systemintegrationsunternehmen zu konsultieren.

Welche Dokumentation wird mit dem Produkt geliefert?

Umfassende Dokumentation, einschließlich eines detaillierten technischen Datenblatts, Schaltplänen und Anleitungen zur Inbetriebnahme, ist für die erfolgreiche Nutzung des HUSP E3050 – SDR-500 Evalboards unerlässlich und wird bereitgestellt.